## **Ambient Light Sensor IC Series**

# Digital 16bit Serial Output Type Ambient Light Sensor IC

BH1780GLI No.09046EAT08

#### Descriptions

BH1780GLI is an digital Ambient Light Sensor IC for  $I^2C$  bus interface. This IC is the most suitable to obtain the ambient light data for adjusting LCD and Keypad backlight power of Mobile phone. It is possible to detect wide range at High resolution. (1 - 65535 lx).

#### Features

- 1) I<sup>2</sup>C bus Interface (F/S mode & Hs mode Support, Slave address: "0101001")

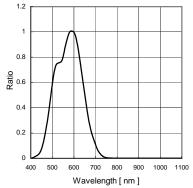

- 2) Spectral responsibility is approximately human eye response

- 3) Illuminance to Digital Converter

- 4) Wide range and High resolution. ( 1-65535 lx )

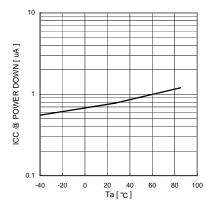

- 5) Low Current by power down function

- 6) 50Hz / 60Hz Light noise reject-function

- 7) 1.8V Logic input interface

- 8) No need any external parts

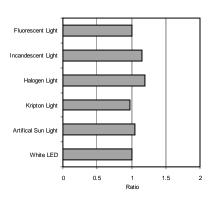

- 9) Light source dependency is little. ( ex. Incandescent Lamp. Fluorescent Lamp. Halogen Lamp. White LED. Sun Light )

- 10) Small measurement variation (+/- 20%)

- 11) The influence of infrared is very small.

#### Applications

Mobile phone, LCD TV, NOTE PC, Portable game machine, Digital camera, Digital video camera, Car navigation, PDA, LCD display

#### Absolute Maximum Ratings

| Parameter             | Symbol | Limits  | Units |

|-----------------------|--------|---------|-------|

| Supply Voltage        | Vmax   | 4.5     | V     |

| Operating Temperature | Topr   | -40~85  | °C    |

| Storage Temperature   | Tstg   | -40~100 | °C    |

| SDA Sink Current      | Imax   | 7       | mA    |

| Power Dissipation     | Pd     | 120※    | mW    |

<sup>※ 70</sup>mm × 70mm × 1.6mm glass epoxy board. Derating in done at 1.6mW/°C for operating above Ta=25°C.

#### Operating Conditions

| Parameter   | Symbol | Min. | Тур. | Max. | Units |

|-------------|--------|------|------|------|-------|

| VCC Voltage | Vcc    | 2.3  | 2.5  | 3.0  | ٧     |

## ● Electrical Characteristics ( VCC = 2.5V, Ta = 25°C, unless otherwise noted )

| Powerdown Current  Measurement Accuracy  Dark ( 0 lx ) Sensor out  Measurement Time  SCL SDA input 'H' Voltage  SCL SDA input 'H' Voltage  SCL SDA input 'H' / 'L' Current  I^2C SDA Output 'L' Voltage  V I^2C Rejected Spike pulse witdh  I^2C Rejected Spike pulse witdh  I^2C Rejected Spike pulse witdh2  SDA SCL Capacitance  I^2C SCL Clock Frequency  I^2C SCL Clock Frequency  I^2C Hold Time ( Repeated ) START Condition  I^2C Hold Time ( Repeated ) START Condition2  I^2C 'L' Period of the SCL Clock  I_2C 'L' Period of the SCL Clock2 | cc1 cc2 cc2 cc2 cc2 cc2 cc2 cc2 cc2 cc2 | -<br>-<br>0.8 | 120<br>0.7 | 200<br>2.5 | uA    | Ev=100 lx ※                            |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|---------------|------------|------------|-------|----------------------------------------|

| Measurement Accuracy  Dark ( 0 Ix ) Sensor out  Measurement Time  SCL SDA input 'H' Voltage  SCL SDA input 'H' Voltage  SCL SDA input 'H' / 'L' Current  I^2C SDA Output 'L' Voltage  V  I^2C Rejected Spike pulse witdh  I^2C Rejected Spike pulse witdh  I^2C Rejected Spike pulse witdh2  SDA SCL Capacitance  I^2C SCL Clock Frequency  I^2C SCL Clock Frequency  I^2C Hold Time ( Repeated ) START Condition  I^2C Hold Time ( Repeated ) START Condition2  I^2C 'L' Period of the SCL Clock  I_2C 'L' Period of the SCL Clock2                   | 5/A<br>50                               | 0.8           |            | 2.5        |       |                                        |

| Dark ( 0 lx ) Sensor out  Measurement Time  SCL SDA input 'H' Voltage  SCL SDA input 'L' Voltage  SCL SDA input 'H' / 'L' Current  I^2C SDA Output 'L' Voltage  V  I^2C Rejected Spike pulse witdh  t  I^2C Rejected Spike pulse witdh  t  SDA SCL Capacitance  I^2C SCL Clock Frequency  I^2C SCL Clock Frequency  I^2C Hold Time ( Repeated ) START Condition  I^2C Hold Time ( Repeated ) START Condition2  I^2C 'L' Period of the SCL Clock  I_2C 'L' Period of the SCL Clock2  I_2C 'L' Period of the SCL Clock2                                  | 50                                      |               | 4.0        |            | uA    | No Input Light                         |

| Measurement Time  SCL SDA input 'H' Voltage  SCL SDA input 'L' Voltage  SCL SDA input 'H' / 'L' Current  I²C SDA Output 'L' Voltage  V  I²C Rejected Spike pulse witdh  t²C Rejected Spike pulse witdh2  SDA SCL Capacitance  I²C SCL Clock Frequency  fs  I²C SCL Clock Frequency2  fs  I²C Hold Time (Repeated) START Condition  I²C Hold Time (Repeated) START Condition2  I²C 'L' Period of the SCL Clock  tL  I²C 'L' Period of the SCL Clock2                                                                                                    |                                         | 0             | 1.0        | 1.2        | Times | Sensor out / Actual lx<br>Ev=1000 lx ※ |

| SCL SDA input 'H' Voltage  SCL SDA input 'L' Voltage  SCL SDA input 'H' / 'L' Current  I^2C SDA Output 'L' Voltage  V  I^2C Rejected Spike pulse witdh  I^2C Rejected Spike pulse witdh2  SDA SCL Capacitance  I^2C SCL Clock Frequency  I^2C SCL Clock Frequency  I^2C Hold Time (Repeated) START Condition  I^2C Hold Time (Repeated) START Condition2  I^2C 'L' Period of the SCL Clock  I_2C 'L' Period of the SCL Clock2  I_2C 'L' Period of the SCL Clock2                                                                                       | N /                                     | 0             | 0          | 2          | count |                                        |

| SCL SDA input 'L' Voltage  SCL SDA input 'H' / 'L' Current  I²C SDA Output 'L' Voltage  V  I²C Rejected Spike pulse witdh  t  I²C Rejected Spike pulse witdh2  SDA SCL Capacitance  I²C SCL Clock Frequency  fs  I²C SCL Clock Frequency2  fs  I²C Hold Time ( Repeated ) START  Condition  I²C Hold Time ( Repeated ) START  Condition2  I²C 'L' Period of the SCL Clock  t  I²C 'L' Period of the SCL Clock2                                                                                                                                         | M                                       | _             | 150        | 250        | ms    |                                        |

| SCL SDA input 'H' / 'L' Current  I^2C SDA Output 'L' Voltage  V  I^2C Rejected Spike pulse witdh  I^2C Rejected Spike pulse witdh2  SDA SCL Capacitance  I^2C SCL Clock Frequency  I^2C SCL Clock Frequency2  I^2C Hold Time (Repeated) START Condition  I^2C Hold Time (Repeated) START Condition2  I^2C 'L' Period of the SCL Clock  I^2C 'L' Period of the SCL Clock2                                                                                                                                                                               | / <sub>ІН</sub>                         | 1.26          | _          | _          | V     |                                        |

| I <sup>2</sup> C SDA Output 'L' Voltage  V  I <sup>2</sup> C Rejected Spike pulse witdh  I <sup>2</sup> C Rejected Spike pulse witdh2  SDA SCL Capacitance  I <sup>2</sup> C SCL Clock Frequency  I <sup>2</sup> C SCL Clock Frequency  fs  I <sup>2</sup> C Hold Time (Repeated) START Condition  I <sup>2</sup> C Hold Time (Repeated) START Condition2  I <sup>2</sup> C 'L' Period of the SCL Clock  I <sup>2</sup> C 'L' Period of the SCL Clock2                                                                                                 | / <sub>IL</sub>                         | _             | -          | 0.54       | V     |                                        |

| I <sup>2</sup> C Rejected Spike pulse witdh  I <sup>2</sup> C Rejected Spike pulse witdh2  SDA SCL Capacitance  I <sup>2</sup> C SCL Clock Frequency  I <sup>2</sup> C SCL Clock Frequency2  I <sup>2</sup> C Hold Time (Repeated ) START Condition  I <sup>2</sup> C Hold Time (Repeated ) START Condition2  I <sup>2</sup> C 'L' Period of the SCL Clock  I <sup>2</sup> C 'L' Period of the SCL Clock2                                                                                                                                              | I <sub>i</sub>                          | -10           | _          | 10         | uA    |                                        |

| I <sup>2</sup> C Rejected Spike pulse witdh2  SDA SCL Capacitance  I <sup>2</sup> C SCL Clock Frequency  I <sup>2</sup> C SCL Clock Frequency2  I <sup>2</sup> C Hold Time (Repeated) START Condition  I <sup>2</sup> C Hold Time (Repeated) START Condition2  I <sup>2</sup> C 'L' Period of the SCL Clock  I <sup>2</sup> C 'L' Period of the SCL Clock2                                                                                                                                                                                             | OL1                                     | 0             | _          | 0.4        | V     | IOL=3 mA                               |

| SDA SCL Capacitance  I²C SCL Clock Frequency  I²C SCL Clock Frequency2  I²C Hold Time (Repeated) START Condition  I²C Hold Time (Repeated) START Condition2  I²C 'L' Period of the SCL Clock  I²C 'L' Period of the SCL Clock2                                                                                                                                                                                                                                                                                                                         | SP                                      | -             | 100        | -          | ns    | F/S mode                               |

| I <sup>2</sup> C SCL Clock Frequency  I <sup>2</sup> C SCL Clock Frequency2  I <sup>2</sup> C Hold Time (Repeated ) START Condition  I <sup>2</sup> C Hold Time (Repeated ) START Condition2  I <sup>2</sup> C 'L' Period of the SCL Clock  I <sup>2</sup> C 'L' Period of the SCL Clock2  I <sup>2</sup> C 'L' Period of the SCL Clock2                                                                                                                                                                                                               | SP                                      | -             | 20         | -          | ns    | Hs mode                                |

| I <sup>2</sup> C SCL Clock Frequency2  I <sup>2</sup> C Hold Time ( Repeated ) START Condition  I <sup>2</sup> C Hold Time ( Repeated ) START Condition2  I <sup>2</sup> C 'L' Period of the SCL Clock  I <sup>2</sup> C 'L' Period of the SCL Clock2  I <sup>2</sup> C 'L' Period of the SCL Clock2                                                                                                                                                                                                                                                   | Ci                                      | -             | 7          | -          | pF    |                                        |

| I²C Hold Time ( Repeated ) START Condition       tHE         I²C Hold Time ( Repeated ) START Condition2       tHE         I²C 'L' Period of the SCL Clock       tL         I²C 'L' Period of the SCL Clock2       tL                                                                                                                                                                                                                                                                                                                                  | SCL                                     | _             | _          | 400        | kHz   | F/S mode                               |

| Condition  I <sup>2</sup> C Hold Time ( Repeated ) START Condition2  I <sup>2</sup> C 'L' Period of the SCL Clock  I <sup>2</sup> C 'L' Period of the SCL Clock2  t <sub>L</sub>                                                                                                                                                                                                                                                                                                                                                                       | CLH                                     | 0             | -          | 3.4        | MHz   | Hs mode Cb=100pF                       |

| $ \begin{array}{c} \text{I}^2\text{C Hold Time (Repeated) START} \\ \text{Condition2} \\ \text{I}^2\text{C 'L' Period of the SCL Clock} \\ \text{I}^2\text{C 'L' Period of the SCL Clock2} \\ \end{array} $                                                                                                                                                                                                                                                                                                                                            | D;STA                                   | 0.6           | _          | _          | us    | F/S mode                               |

| I <sup>2</sup> C 'L' Period of the SCL Clock2 t <sub>L</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | );STA                                   | 160           | -          | -          | ns    | Hs mode                                |

| 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | OW                                      | 1.3           | _          | _          | us    | F/S mode                               |

| J <sup>2</sup> C 'H' Period of the SCL Clock tu                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | OW                                      | 160           | -          | _          | ns    | Hs mode                                |

| I O II I CIIOG OI IIIC OOL OIOOK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | IIGH                                    | 0.6           | _          | _          | us    | F/S mode                               |

| I <sup>2</sup> C 'H' Period of the SCL Clock2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | IGH                                     | 60            | -          | _          | ns    | Hs mode                                |

| I <sup>2</sup> C Set up time for a Repeated START Condition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | J;STA                                   | 0.6           | _          | _          | us    | F/S mode                               |

| I <sup>2</sup> C Set up time for a Repeated START Condition2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | J;STA                                   | 160           | _          | _          | ns    | Hs mode                                |

| I <sup>2</sup> C Data Hold Time t <sub>HE</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | );DAT                                   | 0             | _          | _          | us    | F/S mode                               |

| I <sup>2</sup> C Data Hold Time2 t <sub>HC</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | );DAT                                   | 0             | _          | 70         | ns    | Hs mode Cb=100pF                       |

| I <sup>2</sup> C Data Setup Time t <sub>SU</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | J;DAT                                   | 100           | _          | _          | ns    | F/S mode                               |

| I <sup>2</sup> C Data Setup Time2 t <sub>SL</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | J;DAT                                   | 10            | _          | _          | ns    | Hs mode                                |

| I <sup>2</sup> C Set up Time for STOP Condition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | I;STO                                   | 0.6           | _          | _          | us    | F/S mode                               |

| I <sup>2</sup> C Set up Time for STOP Condition2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | I;STO                                   | 160           | _          | _          | ns    | Hs mode                                |

| I <sup>2</sup> C Bus Free Time between a STOP and START Condition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | BUF                                     | 1.3           | _          | _          | us    |                                        |

| I <sup>2</sup> C Data Valid Time t <sub>VE</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | );DAT                                   | -             | -          | 0.9        | us    | F/S mode                               |

| I <sup>2</sup> C Data Valid Acknowledge Time t <sub>VE</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                         | _             | -          | 0.9        | us    | F/S mode                               |

White LED is used as optical source.

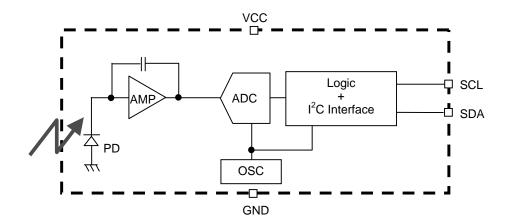

#### Block Diagram

- PD

- Photo diode with approximately human eye response.

- AMP

- Integration-OPAMP for converting from PD current to voltage.

- ADC

- AD converter for obtainment digital 16bit data.

- Logic + I<sup>2</sup>C Interface

- Ambient Light Calculation and I<sup>2</sup>C bus Interface. It is including below register.

- Data Register → This is for registration of Ambient Light Data. Initial Value is "0000\_0000\_0000\_0000".

- OSC

- Internal Oscillator ( typ. 320kHz ). It is CLK for internal logic.

**Technical Note**

#### Reference Data

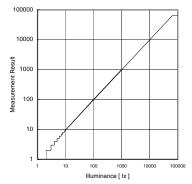

Fig.1 Spectral Response

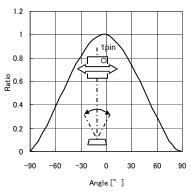

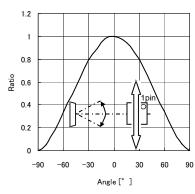

Fig.4 Directional Characteristics 1

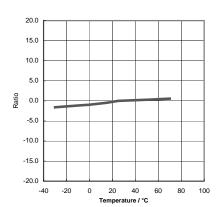

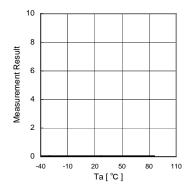

Fig.7 Measurement Result Temperature Dependency

Fig.10 VCC - ICC@0 Lx (POWER DOWN)

Measurement Result 1

Fig.5 Directional Characteristics 2

Fig.8 Light Source Dependency (Fluorescent Light is set to '1')

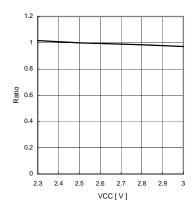

Fig.11 Measurement Result VCC Dependency

Fig.3 Illuminance -Measuremnet Result 2

Fig.6 Dark Response

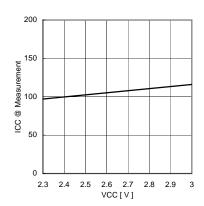

Fig.9 VCC - ICC ( During measurement )

## Command Set

| Address | Register name  | Register function          |

|---------|----------------|----------------------------|

|         | COMMAND        | Specifies register address |

| 0h      | CONTROL        | Control of basic functions |

| Ah      | PART ID        | Part ID                    |

| Bh      | MANUFACTURE ID | Manufacture ID             |

| Ch      | DATALOW        | Low byte of ADC            |

| Dh      | DATAHIGH       | High byte of ADC           |

## O Command Register

| 7   | 6   | 5 | 4 | 3 | 2    | 1    | 0 |

|-----|-----|---|---|---|------|------|---|

| CMD | XXX |   |   |   | ADDF | RESS |   |

default value 00h

| Field   | Bit | Description                                                                                             |

|---------|-----|---------------------------------------------------------------------------------------------------------|

| CMD     | 7   | Write 1                                                                                                 |

| xxx     | 6:4 | Write "000" Don't care if ADDRESS( Command Register< 3 : 0 > ) is "0h" or "Ah" or "Bh" or "Ch" or "Dh". |

| ADDRESS | 3:0 | Register address                                                                                        |

## O Control Register (0h)

| 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-----|-----|-----|-----|-----|-----|-----|-----|

| RES | RES | RES | RES | RES | RES | POV | VER |

default value 00h

| Field | Bit | Description                                                        |  |

|-------|-----|--------------------------------------------------------------------|--|

| RES   | 7:2 | Write "000000"                                                     |  |

| POWER | 1:0 | "00" : Power down<br>"01" : Resv<br>"10" : Resv<br>"11" : Power up |  |

#### O PART ID Register (Ah)

The PART ID register provides device identification. It is a read only register.

| 7       | 6 | 5 | 4 | 3 | 2  | 1   | 0 |

|---------|---|---|---|---|----|-----|---|

| PART NO |   |   |   |   | RI | - v |   |

| Field  | Bit   | Description |

|--------|-------|-------------|

| PARTNO | 7 : 4 | "1000"      |

| REV    | 3:0   | "0001"      |

## O MANUFATCURE ID Register (Bh)

The MANUFACTURE ID register provides device identification. It is a read only register.

| 7              | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |

|----------------|---|---|---|---|---|---|---|--|

| MANUFACTURE ID |   |   |   |   |   |   |   |  |

| Field          | Bit | Description |

|----------------|-----|-------------|

| MANUFACTURE ID | 7:0 | "0000001"   |

## O ADC channel data registers (Ch, Dh)

Illuminance data register.

| 7 | 6 | 5 | 4     | 3        | 2 | 1 | 0 |

|---|---|---|-------|----------|---|---|---|

|   |   |   | CHANN | NEL DATA |   |   |   |

| Register | Address | Bit | Description |

|----------|---------|-----|-------------|

| DATALOW  | Ch      | 7:0 | Lower byte  |

| DATAHIGH | Dh      | 7:0 | Upper byte  |

### Lux calculation

Measurement result is registered to ADC channel data registers(Ch, Dh) in below format.

## DATALOW ( Ch )

| 7                     | 6                     | 5                     | 4              | 3                     | 2                     | 1                     | 0          |

|-----------------------|-----------------------|-----------------------|----------------|-----------------------|-----------------------|-----------------------|------------|

| <b>2</b> <sup>7</sup> | <b>2</b> <sup>6</sup> | <b>2</b> <sup>5</sup> | 2 <sup>4</sup> | <b>2</b> <sup>3</sup> | <b>2</b> <sup>2</sup> | <b>2</b> <sup>1</sup> | <b>2</b> ° |

## DATAHIGH ( Dh )

| I | 7               | 6               | 5                      | 4               | 3   | 2                      | 1                     | 0                     |

|---|-----------------|-----------------|------------------------|-----------------|-----|------------------------|-----------------------|-----------------------|

|   | 2 <sup>15</sup> | 2 <sup>14</sup> | <b>2</b> <sup>13</sup> | 2 <sup>12</sup> | 211 | <b>2</b> <sup>10</sup> | <b>2</b> <sup>9</sup> | <b>2</b> <sup>8</sup> |

This is an example for DATA to Lux convertion when DATA Register values are seeing in below condition. ex)

DATA Low Byte = "1001\_0000" DATA High Byte = "1000\_0011"

$$(2^{15} + 2^9 + 2^8 + 2^7 + 2^4) = 33680 [Ix]$$

|                                          |                                                                                                                   |                                    | from Slave to Mastel         | _        |      |

|------------------------------------------|-------------------------------------------------------------------------------------------------------------------|------------------------------------|------------------------------|----------|------|

|                                          | from Master to Slave                                                                                              |                                    | Irom Slave to Master         |          |      |

| ① Send Pov                               | wer up instruction.                                                                                               |                                    |                              |          |      |

| ST                                       | Slave Address<br>0101001                                                                                          | W ACK                              | Command Register<br>10000000 | AC       | CK   |

|                                          | Co                                                                                                                | ontrol Register ( 0h )<br>00000011 | ACK SP                       |          |      |

| ② Change A                               | ADDRESS Field of Control Re                                                                                       |                                    |                              | _        |      |

| ST                                       | Slave Address<br>0101001                                                                                          | W ACK                              | Command Register<br>10001100 | ACK      |      |

| ③ Read me                                | until Measurement result is ou                                                                                    | nput.                              |                              |          |      |

| ③ Read mea                               |                                                                                                                   | R ACK                              | DATALOW ( Ch )               | ļ        | 40   |

|                                          | asurement result.  Slave Address 0101001                                                                          | R ACK                              | DATALOW ( Ch )               | A        | 40   |

| ST                                       | asurement result.  Slave Address 0101001                                                                          | R<br>1 ACK<br>DATAHIGH ( Dh)       |                              | <i>A</i> | 40   |

| ST S | asurement result.  Slave Address 0101001                                                                          | R<br>1 ACK<br>DATAHIGH ( Dh)       |                              |          | 40   |

| ST S | asurement result.  Slave Address 0101001  ms until measurement result is                                          | R<br>1 ACK<br>DATAHIGH ( Dh)       |                              |          |      |

| Wait 150r      Read mea                  | asurement result.  Slave Address 0101001  ms until measurement result is asurement result.  Slave Address 0101001 | R ACK DATAHIGH ( Dh) s updated.    | ACK SP                       |          |      |

| Wait 150r  Read mea                      | asurement result.  Slave Address 0101001  ms until measurement result is asurement result.  Slave Address 0101001 | R ACK DATAHIGH ( Dh) s updated.    | DATALOW (Ch)                 |          |      |

| Wait 150r  Read mea                      | asurement result.  Slave Address 0101001  ms until measurement result is asurement result.  Slave Address 0101001 | R ACK DATAHIGH ( Dh) s updated.    | DATALOW (Ch)                 |          | 4400 |

- I<sup>2</sup>C Bus Communication

- 1) Slave Address "0101001"

- 2) Main write Format

- 1. Write to Command Register

| ST | Slave Address<br>0101001 | W<br>0 | ACK | Data to Command Register<br>1000XXXX | ACK | SP |  |

|----|--------------------------|--------|-----|--------------------------------------|-----|----|--|

|----|--------------------------|--------|-----|--------------------------------------|-----|----|--|

X Data<7:4> must be "1000"

2. Write to Control Register

| ST | Slave Address<br>0101001 | W<br>0 | ACK | Data to Control Register<br>000000XX | ACK | SP |  |

|----|--------------------------|--------|-----|--------------------------------------|-----|----|--|

|----|--------------------------|--------|-----|--------------------------------------|-----|----|--|

X Data<7:2> must be "000000"

X It is necessary that ADDRESS Field of Command Register must set "0000".

3. Write to Command Register and Control Register

| ST | Slave Address<br>0101001 | W<br>0 | ACK | Command Register<br>1000XXXX | ACK | ] |

|----|--------------------------|--------|-----|------------------------------|-----|---|

|----|--------------------------|--------|-----|------------------------------|-----|---|

| Control Register ( 0h )<br>000000XX | ACK | SP |

|-------------------------------------|-----|----|

|-------------------------------------|-----|----|

3) Main read Format

| ST Slave Address R 1 ACK Data specified at ADDRESS Field of Command Register |

|------------------------------------------------------------------------------|

|------------------------------------------------------------------------------|

| Data specified at ADDRESS Field of Command Register+1 | ACK |  | ACK | Data specified at ADDRESS<br>Field of Command Register +N | IACK | SP |

|-------------------------------------------------------|-----|--|-----|-----------------------------------------------------------|------|----|

|-------------------------------------------------------|-----|--|-----|-----------------------------------------------------------|------|----|

0h - Ah - BH1780GLI outputs Data from specified ADDRESS Field of Command Register until Master issues stop condition.Read cycle is Bh - Ch - Dh - 0h - Ah - Bh - Ch - Dh ........

ex) If ADDRESS Field of Command Register is Ch, then BH1780GLI outputs data like seeing in below. Ch - Dh - Oh - Ah - Bh - Ch - Dh - Oh - Ah .... It is continued until Master issues stop condition.

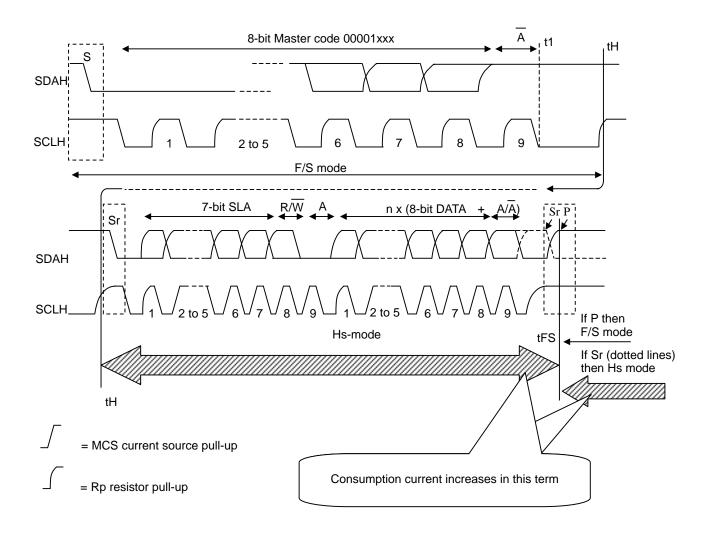

## 4) High speed mode

BH1780GLI supports  $I^2C$  bus High speed mode (Hs-mode). Approximately 80uA is consumped when  $I^2C$  bus is set at Hs-mode. Typical consumption current is seeing in below table.

| State      | F/S mode | Hs-mode | unit |

|------------|----------|---------|------|

| Power down | 0.7      | 80      | uA   |

| Power up   | 120      | 200     | uA   |

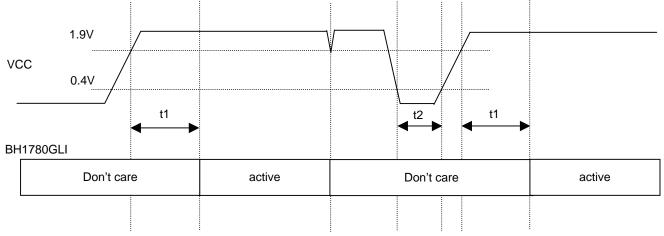

#### Caution of power on reset function

BH1780GLI has power on reset ( POR ) function. POR is to reset all register and flip flop when VCC Power supplies. There is some cautions about power on and down sequence seeing in below.

1 Power on time: t1

More than 2ms is need to active BH1780GLI after VCC supplies more than 1.9V from VCC is less than 0.4V.

#### 2 Power off time : t2

More than 1ms (VCC < 0.4V) is need to active BH1780GLI.

<sup>\*&</sup>quot;active state" is that BH1780GLI works and accept I<sup>2</sup>C bus access correctly.

## Terminal Description

| PIN<br>No. | Terminal Name | Equivalent Circuit | Function                                    |

|------------|---------------|--------------------|---------------------------------------------|

| 1          | VCC           |                    | Power Supply Terminal                       |

| 2          | GND           |                    | GND Terminal                                |

| 3          | SDA           |                    | I <sup>2</sup> C bus Interface SDA Terminal |

| 4          | SCL           |                    | I <sup>2</sup> C bus Interface SCL Terminal |

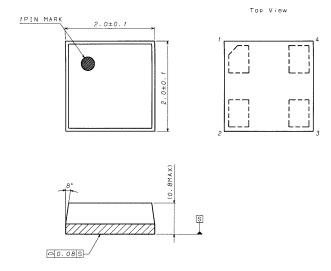

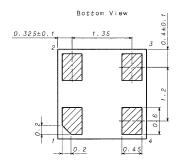

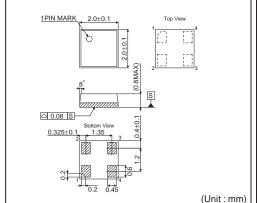

## Package Outlines

(UNIT:mm)

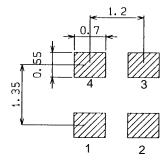

## Recommended Land pattern (Top view)

#### Cautions on use

#### 1) Absolute Maximum Ratings

An excess in the absolute maximum ratings, such as supply voltage (Vmax), temperature range of operating conditions (Topr), etc., can break down devices, thus making impossible to identify breaking mode such as a short circuit or an open circuit. If any special mode exceeding the absolute maximum ratings is assumed, consideration should be given to take physical safety measures including the use of fuses, etc.

#### 2) GND voltage

Make setting of the potential of the GND terminal so that it will be maintained at the minimum in any operating state. Furthermore, check to be sure no terminals are at a potential lower than the GND voltage including an actual electric transient.

#### 3) Short circuit between terminals and erroneous mounting

In order to mount ICs on a set PCB, pay thorough attention to the direction and offset of the ICs. Erroneous mounting can break down the ICs. Furthermore, if a short circuit occurs due to foreign matters entering between terminals or between the terminal and the power supply or the GND terminal, the ICs can break down.

#### 4) Operation in strong electromagnetic field

Be noted that using ICs in the strong electromagnetic field can malfunction them.

#### 5) Inspection with set PCB

On the inspection with the set PCB, if a capacitor is connected to a low-impedance IC terminal, the IC can suffer stress. Therefore, be sure to discharge from the set PCB by each process. Furthermore, in order to mount or dismount the set PCB to/from the jig for the inspection process, be sure to turn OFF the power supply and then mount the set PCB to the jig. After the completion of the inspection, be sure to turn OFF the power supply and then dismount it from the jig. In addition, for protection against static electricity, establish a ground for the assembly process and pay thorough attention to the transportation and the storage of the set PCB.

#### 6) Input terminals

In terms of the construction of IC, parasitic elements are inevitably formed in relation to potential. The operation of the parasitic element can cause interference with circuit operation, thus resulting in a malfunction and then breakdown of the input terminal. Therefore, pay thorough attention not to handle the input terminals; such as to apply to the input terminals a voltage lower than the GND respectively, so that any parasitic element will operate.

## 7) Thermal design

Perform thermal design in which there are adequate margins by taking into account the power dissipation ( Pd ) in actual states of use.

#### 8) Treatment of package

Dusts or scratch on the photo detector may affect the optical characteristics. Please handle it with care.

#### 9) Rush current

When power is first supplied to the CMOS IC, it is possible that the internal logic may be unstable and rush current may flow instantaneously. Therefore, give special consideration to power coupling capacitance, power wiring, width of GND wiring, and routing of connections.

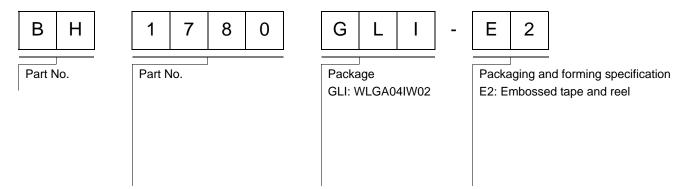

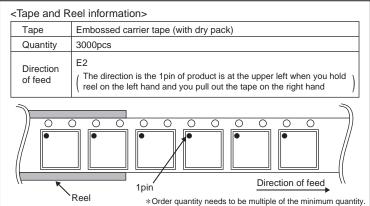

## Ordering part number

#### WLGA04IW02

#### Notes

No copying or reproduction of this document, in part or in whole, is permitted without the consent of ROHM Co.,Ltd.

The content specified herein is subject to change for improvement without notice.

The content specified herein is for the purpose of introducing ROHM's products (hereinafter "Products"). If you wish to use any such Product, please be sure to refer to the specifications, which can be obtained from ROHM upon request.

Examples of application circuits, circuit constants and any other information contained herein illustrate the standard usage and operations of the Products. The peripheral conditions must be taken into account when designing circuits for mass production.

Great care was taken in ensuring the accuracy of the information specified in this document. However, should you incur any damage arising from any inaccuracy or misprint of such information, ROHM shall bear no responsibility for such damage.

The technical information specified herein is intended only to show the typical functions of and examples of application circuits for the Products. ROHM does not grant you, explicitly or implicitly, any license to use or exercise intellectual property or other rights held by ROHM and other parties. ROHM shall bear no responsibility whatsoever for any dispute arising from the use of such technical information.

The Products specified in this document are intended to be used with general-use electronic equipment or devices (such as audio visual equipment, office-automation equipment, communication devices, electronic appliances and amusement devices).

The Products specified in this document are not designed to be radiation tolerant.

While ROHM always makes efforts to enhance the quality and reliability of its Products, a Product may fail or malfunction for a variety of reasons.

Please be sure to implement in your equipment using the Products safety measures to guard against the possibility of physical injury, fire or any other damage caused in the event of the failure of any Product, such as derating, redundancy, fire control and fail-safe designs. ROHM shall bear no responsibility whatsoever for your use of any Product outside of the prescribed scope or not in accordance with the instruction manual.

The Products are not designed or manufactured to be used with any equipment, device or system which requires an extremely high level of reliability the failure or malfunction of which may result in a direct threat to human life or create a risk of human injury (such as a medical instrument, transportation equipment, aerospace machinery, nuclear-reactor controller, fuel-controller or other safety device). ROHM shall bear no responsibility in any way for use of any of the Products for the above special purposes. If a Product is intended to be used for any such special purpose, please contact a ROHM sales representative before purchasing.

If you intend to export or ship overseas any Product or technology specified herein that may be controlled under the Foreign Exchange and the Foreign Trade Law, you will be required to obtain a license or permit under the Law.

Thank you for your accessing to ROHM product informations. More detail product informations and catalogs are available, please contact us.

# ROHM Customer Support System

http://www.rohm.com/contact/